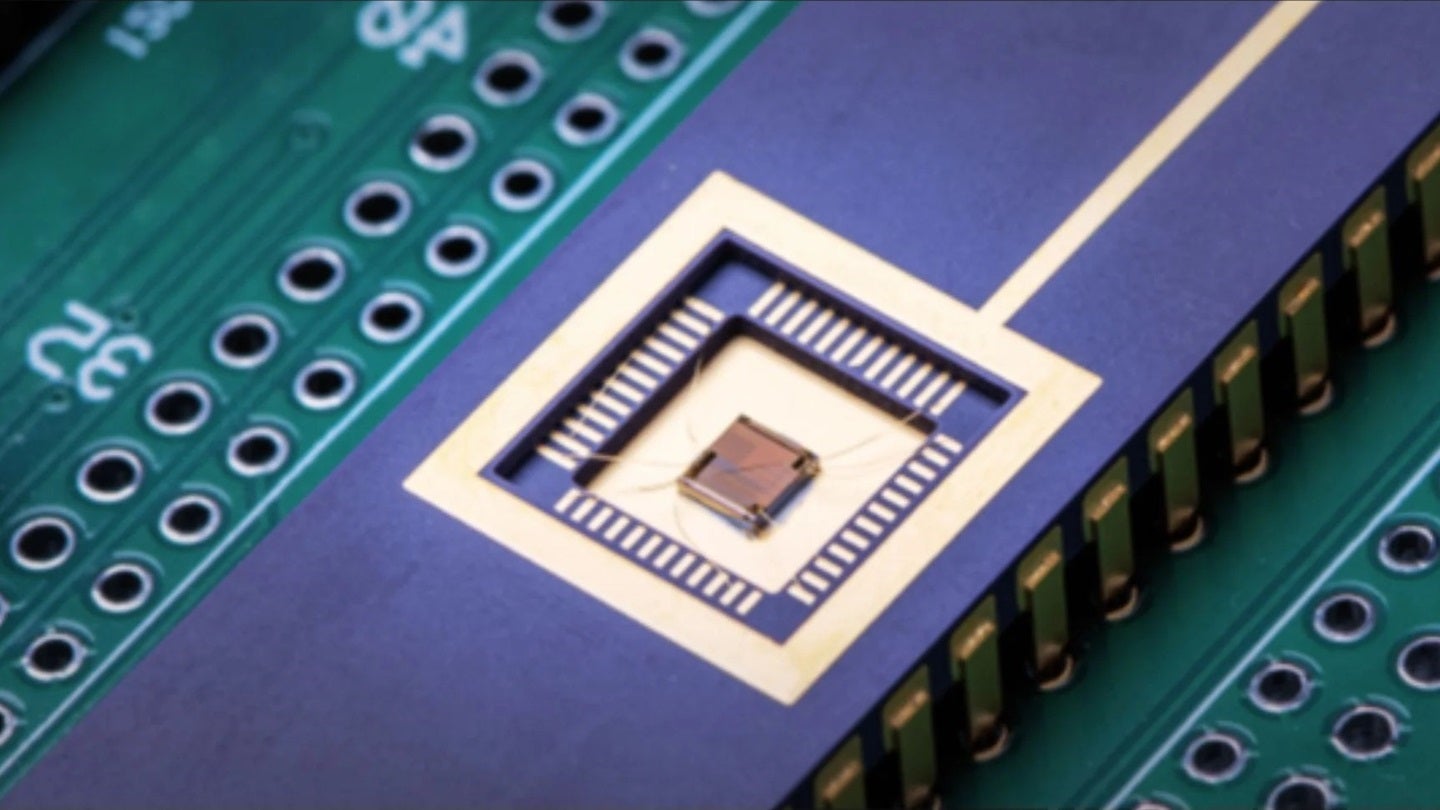

SEALSQ has introduced the Quantum Shield QS7001 silicon chip at the IQT Quantum+AI 2025 Conference in New York City.

According to the company, the QS7001 is the first silicon chip to integrate post-quantum cryptography (PQC) algorithms standardised by the US National Institute of Standards and Technology (NIST) directly into its hardware.

Access deeper industry intelligence

Experience unmatched clarity with a single platform that combines unique data, AI, and human expertise.

The post-quantum chip will become commercially available in mid-November 2025. Customers will have access to development kits upon the product’s launch.

The QS7001 integrates ML-KEM (CRYSTALS-Kyber) and ML-DSA (CRYSTALS-Dilithium) algorithms at the hardware level.

SEALSQ noted that this approach avoids reliance on software-based cryptographic execution and is intended to address security requirements emerging from quantum computing threats.

The chip supports open hardware design, accommodates custom firmware, and provides an option for hybrid cryptography migration.

In addition to the Quantum Shield QS7001, SEALSQ plans to release QVault Trusted Platform Module (TPM) variants, expanding its offerings in secure hardware solutions, starting in the first half of 2026.

NIST finalised its post-quantum standards in August 2024, choosing Kyber, Dilithium and SPHINCS+ as the primary methods to protect against quantum-enabled decryption of Elliptic Curve Cryptography (ECC) and Rivest Shamir Adleman (RSA).

These standards join a series of regulatory initiatives, including US CNSA 2.0 and White House executive orders mandating PQC adoption by 2030.

Similar requirements from the EU and allied countries target a 2026–2030 migration window across sectors such as finance, healthcare, infrastructure, and Internet of Things (IoT).

SEALSQ is among a small number of companies with Common Criteria EAL5+ and FIPS 140-3 security certification for its hardware.

The company provides device personalisation through secure centres in Switzerland and France, with expansion planned in Spain, India, and the US. SEALSQ reported a deployment history exceeding 1.75 billion devices.

Targeted applications for the QS7001 include defence systems, aerospace, healthcare infrastructure, energy distribution, smart grids, and large-scale IoT authentication.

SEALSQ CEO Carlos Moreira said: “By embedding post-quantum cryptography directly in hardware, this chip aims to set a new paradigm of trust and protection, securing sovereign infrastructure, healthcare, energy systems, and connected devices against the coming quantum threat.”

Meanwhile, SEALSQ is integrating its recent acquisition of the French application-specific integrated circuit (ASIC) design house IC’Alps. The company stated that this strategy will enable it to offer catalogue ICs, custom ICs, and security intellectual property (IP), all within a unified roadmap.

Immediate plans include commercial rollout of the PQC chip, followed by development of custom quantum ASICs (QASIC) and related IP, with longer-term efforts aimed at system-level solutions for next-generation architectures such as chiplet-based security modules.

The QASIC programme will serve as a basis for SEALSQ’s future post-quantum hardware security modules and secure microcontrollers, with focus areas including critical infrastructure, defence, IoT, and AI systems.

In September 2025, SEALSQ and Kaynes SemiCon signed a term sheet to form SEALKAYNESQ, a joint venture to build India’s first secure semiconductor design and personalisation centre.