MegaChips has filed a patent for a semiconductor device that includes multiple silicon layers separated by oxide layers. The device features a cavity within one of the silicon layers, which can be sealed using a metal feature within a passageway. The patent claim has been canceled. GlobalData’s report on MegaChips gives a 360-degree view of the company including its patenting strategy. Buy the report here.

Access deeper industry intelligence

Experience unmatched clarity with a single platform that combines unique data, AI, and human expertise.

According to GlobalData’s company profile on MegaChips, Cloud gaming was a key innovation area identified from patents. MegaChips's grant share as of September 2023 was 49%. Grant share is based on the ratio of number of grants to total number of patents.

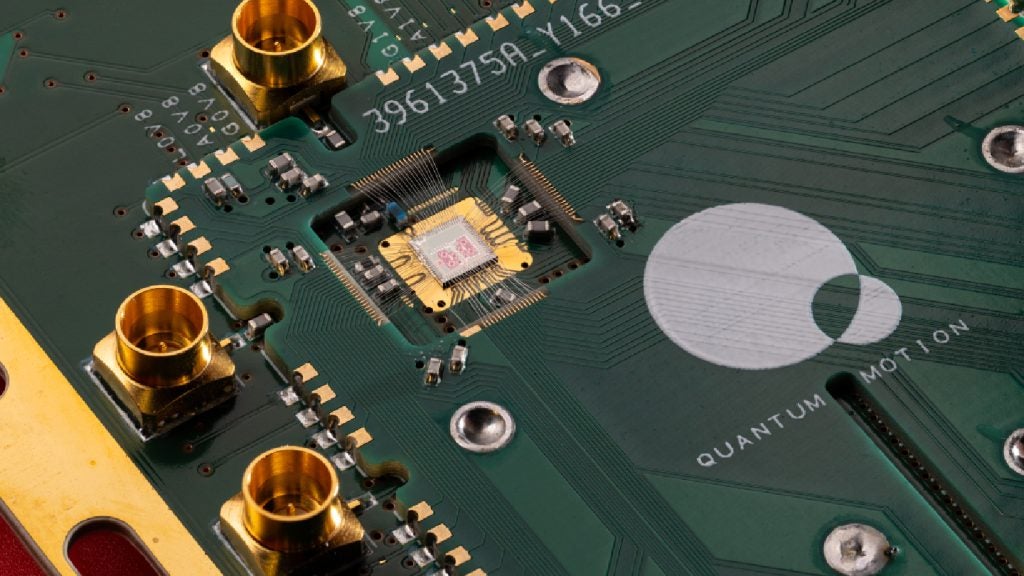

Semiconductor device with hermetically sealed cavity

A recently filed patent (Publication Number: US20230286798A1) describes an integrated circuit with unique features. The circuit includes a layer stack consisting of a first silicon layer, a second silicon layer, and an oxide layer between them. Within this layer stack, there is a chamber and a microelectromechanical systems (MEMS) component with a piezoelectric layer. An electrode is also present, along with a conductive path that connects the electrode to an electrical contact on the exterior surface of the circuit. This conductive path provides an output signal representing the motion sensed by the MEMS component.

To allow for movement of the MEMS component, a passageway is formed through either the first or second silicon layer. This passageway has at least one bend to prevent a line-of-sight view through the layer. The chamber is created by removing oxide from the oxide layer via the passageway, allowing the MEMS component to freely move or deflect within it. To prevent the ingress of materials into the chamber, at least one material is deposited to block the passageway. The bend in the passageway inhibits the deposition of this material into the chamber.

The patent also mentions various options for the materials used in the circuit. The blocking material can be a non-metal, epitaxial silicon, or a metal such as tungsten. The passageway is characterized by a ratio of its length perpendicular to the layer stack to its minimum width, with the ratio being equal to or greater than five. The minimum width of the passageway is less than or equal to two microns. An oxide layer can be used to encapsulate the blocking material relative to the exterior surface of the circuit.

Additionally, the patent describes a method for fabricating the integrated circuit. The method involves providing the layer stack, forming the chamber, placing the MEMS component, creating the conductive path, and forming the passageway with at least one bend. The chamber is formed by removing oxide via the passageway, and then the passageway is blocked with at least one material. The deposition of this material is inhibited by the bend in the passageway. The method also includes options for the materials used, such as non-metal, epitaxial silicon, or metal deposition.

In summary, this patent describes an integrated circuit with a unique design that allows for the movement of a MEMS component within a chamber. The circuit includes a layer stack, passageway with a bend, and various options for materials used. The method for fabricating the circuit is also outlined in the patent.

To know more about GlobalData’s detailed insights on MegaChips, buy the report here.

Data Insights

From

The gold standard of business intelligence.

Blending expert knowledge with cutting-edge technology, GlobalData’s unrivalled proprietary data will enable you to decode what’s happening in your market. You can make better informed decisions and gain a future-proof advantage over your competitors.